I hope you have completed Part 2 of the Experiment and is ready for Part 3.

In part 3, you are going to use the FPGA to interface with the external world through a DAC and a ADC on the add-on card. You will also learn about FSM design and PWM module. Finally the DAC and ADC use a serial interface known as SPI. We will take a brief look at this interface standard without going into details of how to write Verilog to specify the SPI module design.

Here again is a list of topics covered in this lecture. The we basically will cover three things: PWM, FSM design and SPI for interfacing. All these are relevant to Part 3 of the Experiment for this week.

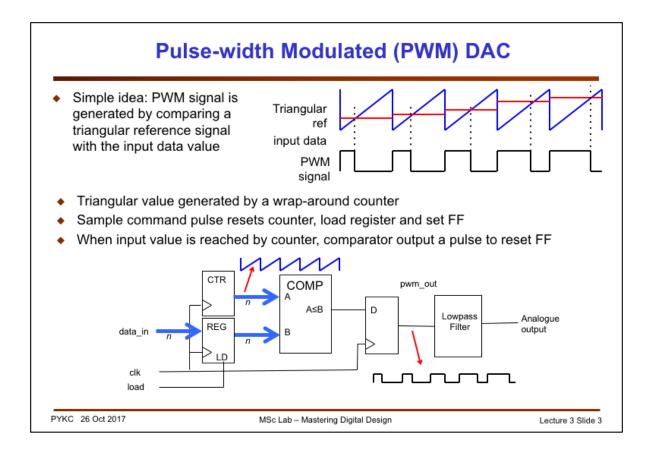

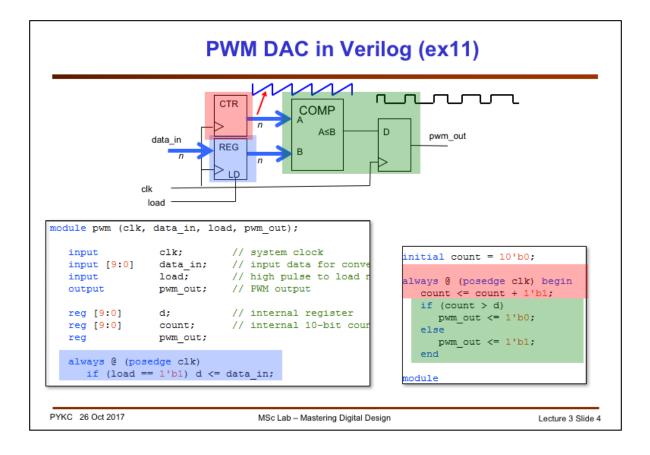

Instead of using analogue resistor network, it is possible to build a simple DAC using only digital components.

Here is a circuit schematic for a pulse-width modulated DAC. Here the counter is used to produce a count value A that ramps up linearly in a sawtooth manner. The digital value we want to convert to analogue value is data\_in, which is stored as B in the input register. A digital comparator circuit compares this input data with the counter value (which is ramping up). While A is less than B, the output of the comparator is high. As soon as A exceeds B, the output goes low. In this way, the pulse width is proportional to the value of B (or data\_in) in a linear manner. Passing this PWM signal through a lowpass filter will give an analogue output which is linearly related to data\_in.

This is how the PWM module works. It is very simple, but very effective. You should compare the DAC output and PWM output in Part 3 of the experiment, and see that the two methods are equally effective in producing an analogue voltage.

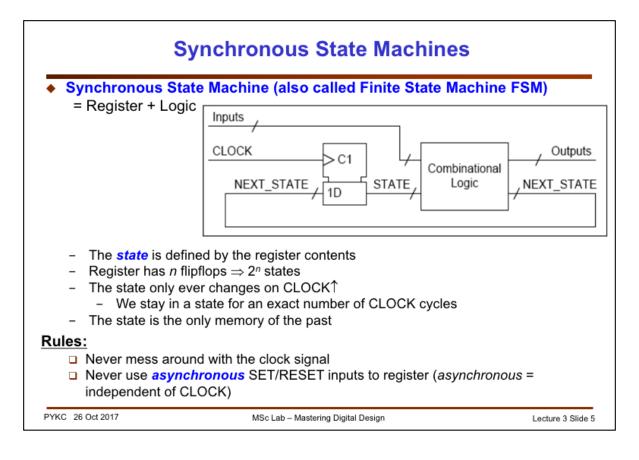

Here is a simplified generic diagram of a finite (or synchronous) state machine (FSM or SSM). A set of D-flipflips are used to store the current state value. The current state together with external inputs are fed to a combinational logic circuit to evaluate two things: the **next state** and the **current outputs**.

With an n-bit register and using binary state encoding (i.e. coding states as binary number), such machine can have a maximum of 2<sup>n</sup> states.

This is a synchronous state machine because the transition to the next state is synchronous with the rising edge of the clock signal. Therefore all output signals are synchronized.

There are two basic rules in designing a FSM that operates reliably: 1.Do not put logic in front of the clock signal. Doing so is likely to cause timing issues when the SSM is used in conjunction with the rest of the system. 2.Do not use asynchronous SET or RESET signals. Doing so would make the rest of the system NOT synchronous to the CLOCK signal.

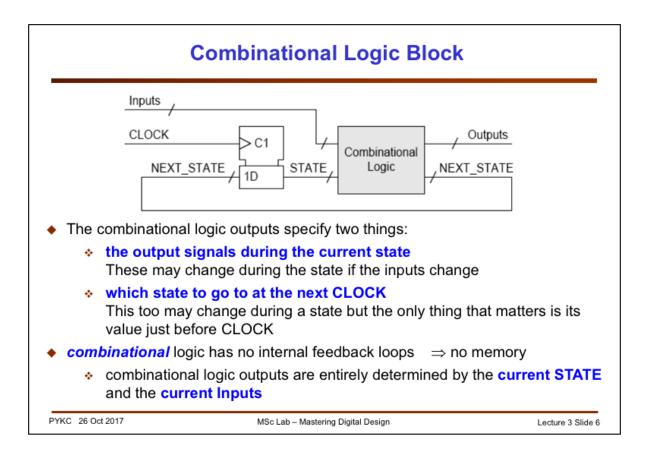

The combinational logic circuit in a FSM performs two separate tasks:

- 1. It determines what **the output signals** should be. This derived by the current state value STATE and the current inputs. Therefore such output signals could change in the middle of a clock cycle if input signals are NOT synchronized with the CLOCK.

- 2. It determines what the **next state value** should be, i.e. the state transition of the FSM.

The combinational logic block (by definition) contains no memory (or register) circuit.

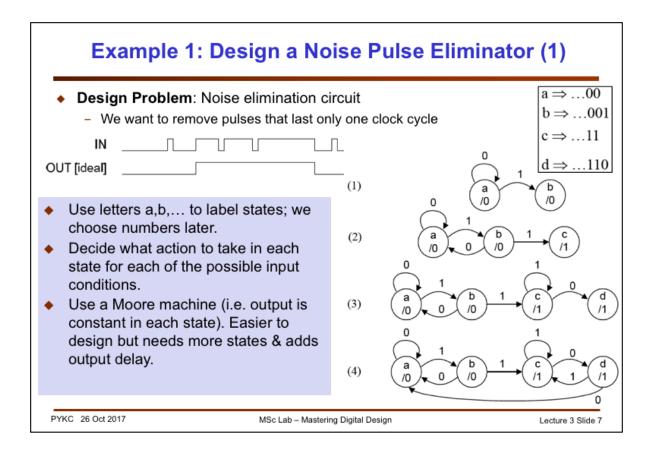

We will now consider the design of a FSM to do some defined function: Design a circuit to eliminate noise pulses. A noise pulse (high or low) is one that lasts only for one clock cycle. Therefore, in the waveform shown above, IN goes from low to high, but included with some high and some low noise pulses. The goal is to clean this up and produce ideally the output OUT as shown.

Here we label the states with letters **a**, **b**, **c** .... Starting with a when IN = 0, and we are waiting for  $IN \rightarrow 1$ . Then we transit to **b**. However, this could be a noise pulse. Therefore we wait for IN to stay as 1 for another close cycle before transiting to **c** and output a 1. If IN goes back to zero after one cycle, we go to **a**, and continue to output a 0.

Similar for state **c**, where we have detect a true 1 for IN. If IN -> 0, we go to **d**, but wait for another cycle for IN staying in 0, before transiting back to state **a**.

Therefore this FSM has four states. Note that in reality, OUT is delayed by ONE clock cycle. There is in fact no way around this – we have to wait for two cycles of IN=0 or IN=1 before deciding on the value of OUT.

| 1. | high for only one clo<br>for ages" and "IN low                                                                                                                                                                                                                                                                                                                     | for two (or more) clock cycles then OUT must go high, whereas if it goes<br>ne clock cycle then OUT stays low. It follows that the two histories "IN low<br>'IN low for ages then high for one clock" are different because if IN is high<br>ock we need different outputs. Hence we need to introduce state b. |                                                                                                                     |        |  |  |  |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|--------|--|--|--|

| 2. | If IN goes high for one clock and then goes low again, we can forget it ever changed at all.<br>This glitch on IN will not affect any of our future actions and so we can just return to state<br>a.<br>If on the other hand we are in state b and IN stays high for a second clock cycle, then the<br>output must change. It follows that we need a new state, c. |                                                                                                                                                                                                                                                                                                                 |                                                                                                                     |        |  |  |  |

| 3. | The need for state d                                                                                                                                                                                                                                                                                                                                               | eed for state d is exactly the same as for state b earlier. We reach state d at the end<br>butput pulse when IN has returned low for one clock cycle. We don't change OUT yet<br>se it might be a false alarm.                                                                                                  |                                                                                                                     |        |  |  |  |

|    |                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                 | ine electro speler tre controlleringe e                                                                             | Ulye   |  |  |  |

| 4. | because it might be<br>If we are in state d a<br>the pulse and OUT                                                                                                                                                                                                                                                                                                 | a false alarm.<br>and IN remains low for a seco                                                                                                                                                                                                                                                                 | nd clock cycle, then it really is the e<br>le pulse ever existed and just return                                    | end of |  |  |  |

| 4. | because it might be<br>If we are in state d a                                                                                                                                                                                                                                                                                                                      | a false alarm.<br>and IN remains low for a seco<br>must go low. We can forget th                                                                                                                                                                                                                                | nd clock cycle, then it really is the e<br>be pulse ever existed and just return<br>ticular history that we need to | end of |  |  |  |

| 4. | because it might be<br>If we are in state d a<br>the pulse and OUT                                                                                                                                                                                                                                                                                                 | a false alarm.<br>and IN remains low for a seco<br>must go low. We can forget th<br>Each state represents a par                                                                                                                                                                                                 | nd clock cycle, then it really is the e<br>be pulse ever existed and just return<br>ticular history that we need to | end of |  |  |  |

This example illustrates how each state represents a particular history that needs to be recorded.

This slide reiterates who we arrives at the state diagram and what each state means.

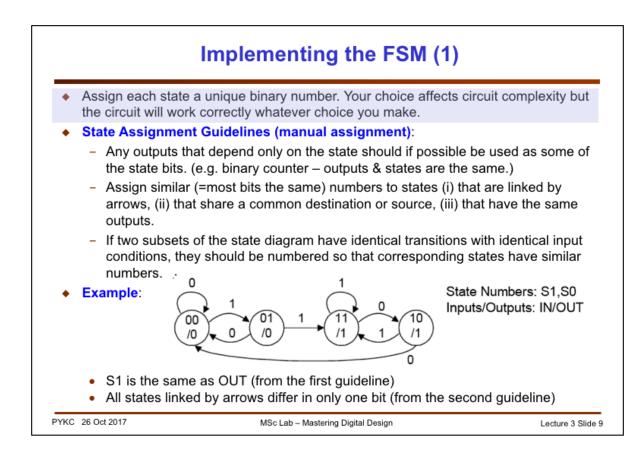

Before mapping the state diagram to hardware, we need to perform **state encoding** – giving each state a unique binary value. For the noise eliminator, we have four states and therefore if we use binary encoding, we need two state bits to encode all four states. Here we assign values S1:S0 of 00, 01, 11 and 10 to states a, b, c and d respectively.

Note that you could assign ANY binary number to any state – and the implemented FSM will work. However, different state encoding will result in different implementations, affecting the complexity of the digital logic.

In the assignment above, we deliberating make S1 the same as OUT – this simplifies the output logic.

We deliberately make all states linked by arrows only having one bit changing (hence  $01 \rightarrow 11$ ). This tends to simply the transition logic and reduce glitches.

|      | Implementing the FSM (2)                                                                                                                                                       |              |              |    |       |      |            |  |  |  |  |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--------------|----|-------|------|------------|--|--|--|--|

|      | <ul> <li>Now we can draw a Karnaugh map (really three K-maps in one) giving NS1, NS0 and OUT in terms of S1, S0 and IN:</li> <li>0</li> <li>1</li> <li>1</li> <li>1</li> </ul> |              |              |    |       |      |            |  |  |  |  |

|      | NS                                                                                                                                                                             | 1,NS0/OU     | JT           | /0 |       |      |            |  |  |  |  |

|      | S1,S0                                                                                                                                                                          | IN=0         | IN=1         |    |       |      | 0          |  |  |  |  |

|      | 00<br>01                                                                                                                                                                       | 00/0<br>00/0 | 01/0<br>11/0 |    | S1,S0 | IN=0 | 51<br>IN=1 |  |  |  |  |

|      | 11                                                                                                                                                                             | 10/1         | 11/1         |    | 00    | 0    | 0          |  |  |  |  |

|      | 10                                                                                                                                                                             | 00/1         | 11/1         |    | 01    | 0    | 1          |  |  |  |  |

|      | -                                                                                                                                                                              |              |              |    | 11    | 1    | 1          |  |  |  |  |

|      |                                                                                                                                                                                |              |              |    | 10    | 0    | 1          |  |  |  |  |

| РҮКС | PYKC 26 Oct 2017 MSc Lab – Mastering Digital Design                                                                                                                            |              |              |    |       |      |            |  |  |  |  |

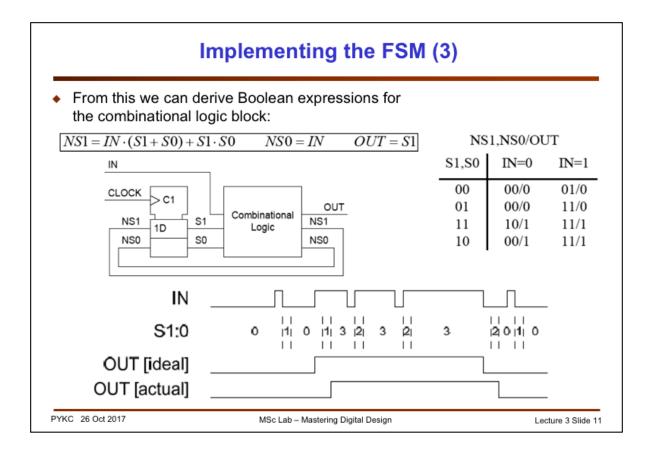

Once we have completed state encoding, we can fill in the state transition table with binary values for the current state values S1:0, the next state values NS1:0 and the output OUT. This is shown on the left.

If you were to design this FSM by hand, you would need to generate Boolean equations for the next state values NS1 and NS2, and the output signal OUT. You may even use K-map to perform Boolean simplification.

Now we can derive the Boolean express for NS1, NS0 and OUT in the usual way.

Since in general FPGA architecture, the logic elements can handle many inputs (at least 4 input signals) and is much more complex than a simple logic gate, implementing the Boolean equation for NS1 would only use ONE logic block. Furthermore, each logic element also include its own registers. So implementing FSM in FPGAs is easy and efficient.

Note that the actual output waveforms shows that OUT has a one clock cycle delay.

## **One-hot encoding**

- Instead of using binary encoding, which works very well in the noise eliminator example, an alternative is to use one-hot encoding.

- In one-hot encoding, each state is encode with a binary value that has a single '1' bit and the rest of the binary variables are '0'.

- Therefore, for the noise eliminator SSM, the states could be encoded as:

- a = 0001 b = 0010 c = 0100 d = 1000

- Using one-hot encoding would use MORE state registers. For N-states, we would need to use N flipflops.

- The advantage is that the state transition and output logic could be much simpler than using binary encoding. There is no longer need for logic to decode the binary number.

- Since FPGAs are a register-rich architecture (each FF is preceded by a small block of logic in the form of a 4-LUT or an ALM), using one-hot encoding could result in simpler and fast SSM implementations.

| РҮКС | 26 Oct 20 | 17 |

|------|-----------|----|

|      |           |    |

MSc Lab – Mastering Digital Design

Lecture 3 Slide 12

In implementing FSMs using FPGAs, we often use a form of state encoding different from simple **binary encoding**. It is known as **one-hot encoding**. With **one-hot encoding**, only one-bit in the state value is "hot" (i.e. set to '1'), and all the other bits are "cold" (i.e. reset to '0').

Using one-hot encoding matches the FPGA architecture well. Each FPGA logic element contains a combinational logic module and one or more registers. Therefore FPGA is a register-rich architecture.

As an exercise, please implement the noise eliminator using one-hot encoding instead of binary encoding as we have in the previous slides by hand (i.e. without using CAD tools). You will appreciate why one-hot encoding is efficient with FPGAs.

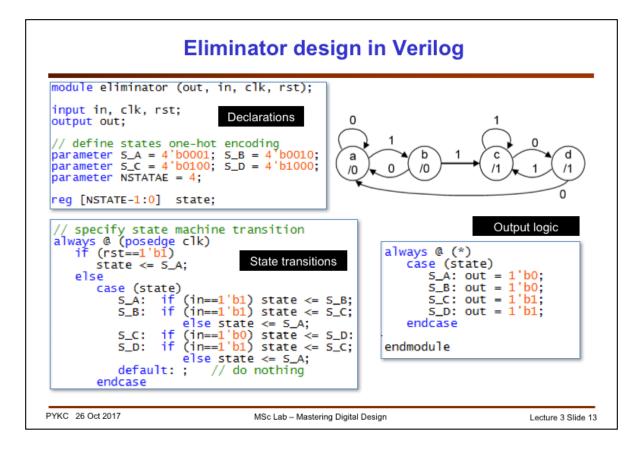

Instead of manually designing a state machine, we usually rely on Verilog specification and synthesis CAD tools such as Altera's Quartus software. Here we use an EXPLICIT reset signal **rst** to put the state machine in a known state. We also use **one-hot** instead of binary encoding of the states. This is specified in the **parameter block**.

Using parameter block to give a name to each of the states has many benefits: the Verilog design is much easier to read; you can change state assignment values without needing to change any codes. In general, parameter block allows you to use **symbols** (names) to replace **numbers**. This makes the code easier to read and easier to maintain, and it is a good habit to get into.

The state variable declaration **reg [NSTATE-1:0]** is used here to show that you there are 4 states (S\_A to S\_D).

When specifying FSM in Verilog, you should following the following convention:

Use always @ (posedge clk) block to specify the state transition. Note that we use the <= assignments (non-blocking) in this always block because you are responding to clock edges.</li>

• Use a separate always @ (\*) block to specify the the output logic. We use normal assignments (blocking) here because this is actually a combinational logic block, not sequential circuit.

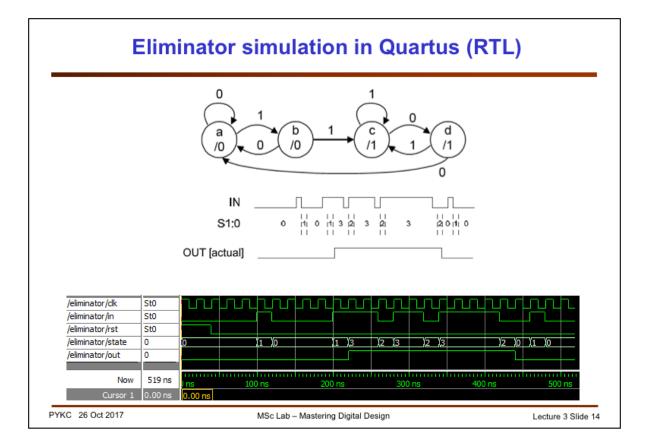

If you enter this Verilog description into Quartus and simulate the circuit, you will see the waveform as shown in this timing diagram as expected. Note that the actual waveform for out is NOT the ideal waveform, but is delayed by one clock cycle.

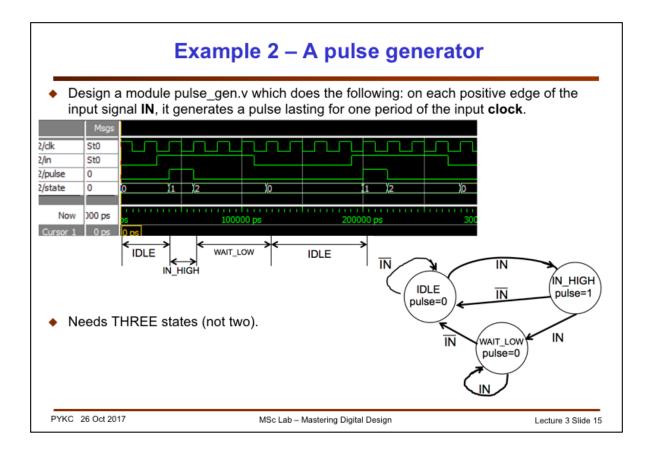

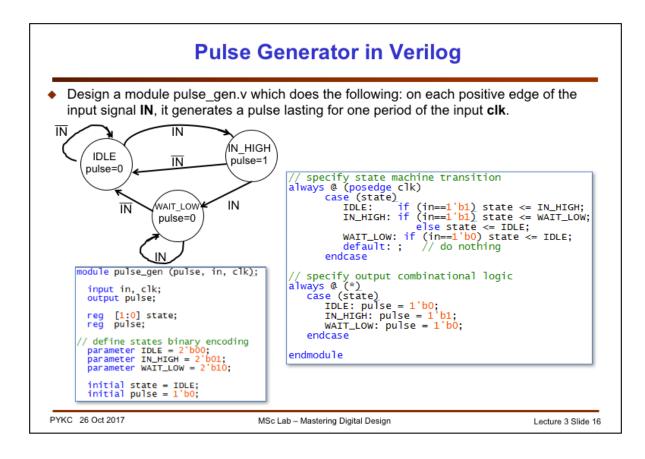

Let us now consider another example, which will appear in the Lab Experiment later. You are required to design a pulse generator circuit that, on the positive edge of the input **IN**, a pulse lasting for one clock period is produced.

The state diagram for this circuit is shown here. There has to be three state: IDLE (waiting for IN to go high), the IN\_HIGH state when a rising edge is detected for IN, and WAIT\_LOW state, where we wait for the IN to go low again.

Shown here is the timing diagram for this design. This module is very useful. It effective detects a rising edge of a signal, and then produces a pulse at the output which is one clock cycle in width.

This FSM has three states: IDEL, IN\_HIGH and WAIT\_LOW. Mapping the state diagram to Verilog is straight forward.

**1.The declaration part** is standard. This is followed by the **parameter section**.. Here we use straight forward binary number assignment, and therefore we have two state bits (maximum four states, but only three are used).

**2.The initial section** is for initialization. Normally for a FSM design, it is best to include a RESET input signal which, when asserted, will synchronously put the state machine to an initial state. Here we are using a nice feature of FPGAs, which allows the digital circuits to be initialised to any states during CONFIGURATION (i.e. when downloading the bit-stream). When you configure the FPGA, the registers used for state[1:0] will be loaded with the value 2'b00The actual state machine is specified with the always @ block.

3. The first line defines the **default output value** for pulse is 0. This ensures that pulse is always defined.

4.The case statement is the best way to specify a FSM. Each case specifies both the conditions for state transitions and the output. It is important to note that state and output specified for each CASE are the next state and next output. For example, if the FSM is in the IDLE state and in==1'b1 on the next positive edge of clk, the FSM will go to state IN\_HIGH and make pulse go high.

5.The <= assignment specifies that the changes will occur simultaneously when the always @ block is exited.

6. Finally, the default section will catch all unspecified cases. In this case, default section is empty (i.e. by default, do nothing). YOU MUST ALSO INCLUDE THE DEFAULT SECTION IN YOUR FSM DESIGN.

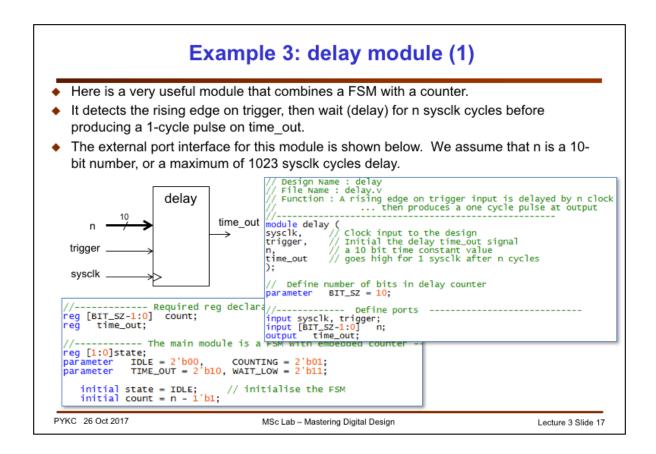

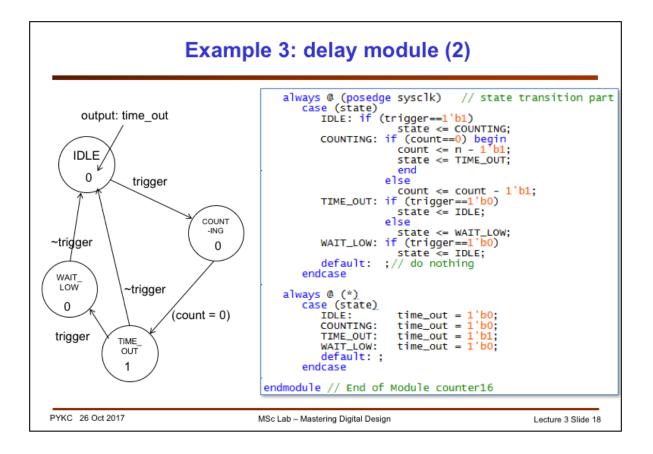

Finally, here is a very useful module that uses a four -state FSM and a counter. It is the combination of the previous example with a down counter embedded inside the FSM. The module detects a rising edge on the trigger input, internally counts **n** clock cycles, then output a pulse on time\_out. This effectively delay the trigger rising edge by n clock cycles. Here we have the port interface and the declaration parts of the Verilog design.

The FSM state diagram is very similar to that for pulse\_gen.v. However we have four states instead of three. Go through this yourself and make sure that you understand how this works.

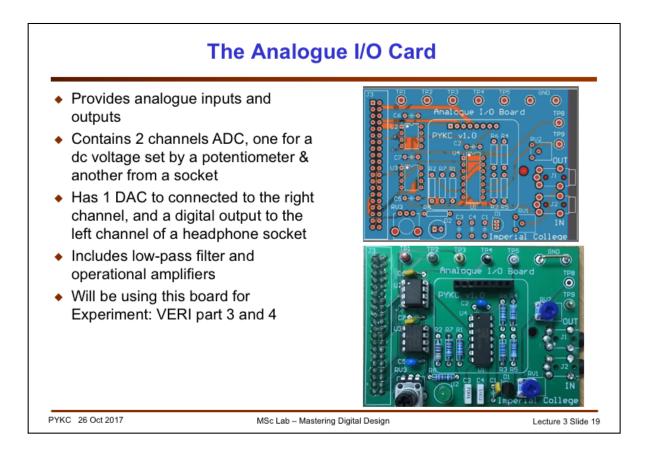

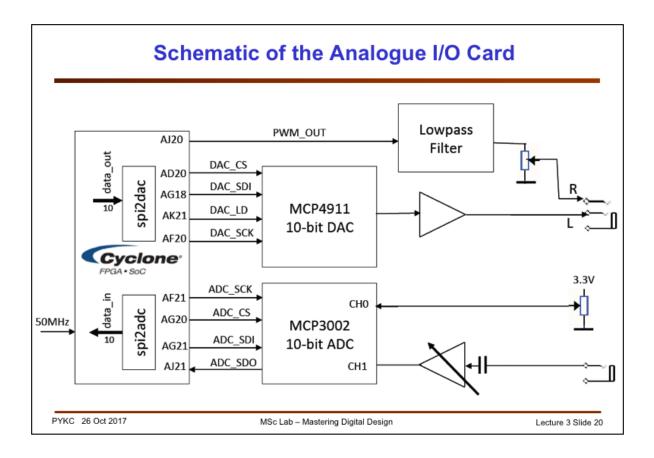

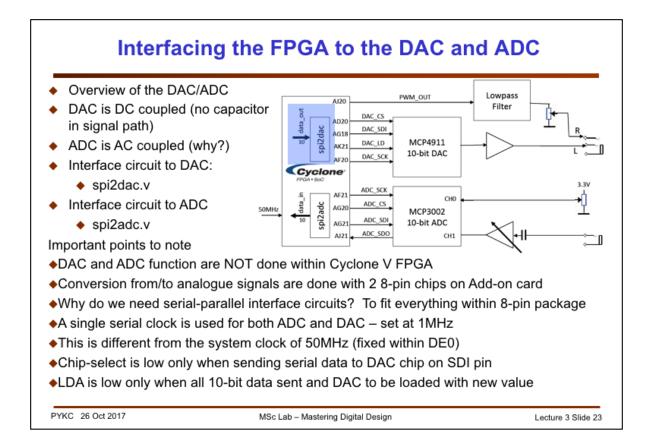

I also provide a purpose-built ADC/DAC board to support the lab experiment. This analogue I/O board in only needed for Part 3 and 4 of VERI. However I will now be examining the digital serial interface for these converter chips.

This shows the block diagram of the analogue I/O card used in the VERI experiment. It consists of a DAC (MCP4911) and a ADC (MCP3002), both using Serial Peripheral Interface (SPI). The DAC output is buffered by a unity gain opamp connected to the right channel of a stereo jack socket.

The ADC has two input channels, one from a potentiometer providing a dc voltage (CH0) and another from the 3.5mm jack socket (CH1).

Finally, there is a 2<sup>nd</sup> order low-pass active filter, the input of which is driven directly from a digital output pin of the Cyclone FPGA. This is intended to provide filtering of a pulse-width modulated DAC output from the FPGA.

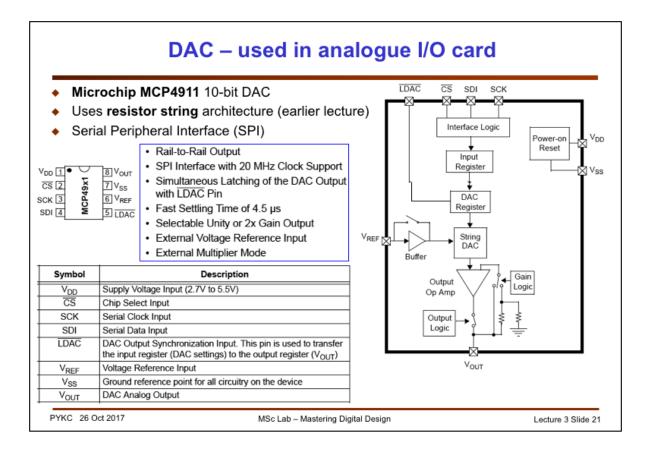

The DAC used with the I/O card is 10-bit, and it uses the Serial Peripheral interface. Its functional block diagram is shown here. The SPI interface has four signals, which should be drive by either the microcontroller or the FPGA. The DAC itself uses a resistor string architecture (i.e. just a bunch of 1024 series resistors of identical values). It has a selectable gain of 1X or 2X.

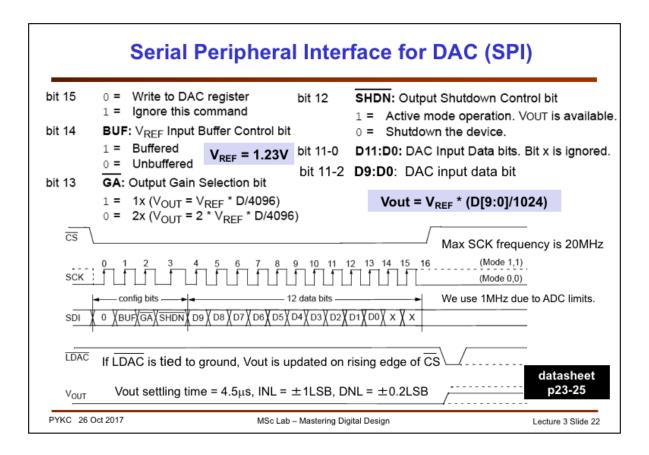

To send a value to the DAC to output (i.e. produce the analogue output Vout), a 16bit value is sent to the DAC chip in a serial manner. The Chip Select (SC) signal going low indicate that this is the start of the data. This establishes the beginning of the data frame. First data bit (bit 15) is always 0. Bit 14 determines whether the reference voltage (Vreg) is buffered or not buffered (via an internal opamp). For our design, Vref is around 3.3V.

Bit 13 determines the gain of the DAC (x1 or x2). Bit 12 is set to 1 if you are using the DAC, and set to 0 if you want to shutdown the device to conserve power. Bit 11 to 2 contains the 10-bit data D[9:0] to convert into analogue voltage Vout, MSB first. Bit 1 and 0 are don't cares.

The LDAC (low active) signal can be connected to ground or used a low active strobe signal to transfer the data to the DAC register (i.e. tell the DAC to update Vout). If LDAC is low, DAC update happens on rising edge of CS\_bar.

This is a simplified diagram showing how the Cyclone V FPGA is interfaced to the two data converters. There are two ADC channels and in our experiment, we are mostly using channel 1 via the 3.5mm jack socket. You will be supplying speech signals from the desktop computer.

There is one DAC which drives both the small speaker and, much better, drives the ear-phone. (Please bring the ear-phone to the lab.)

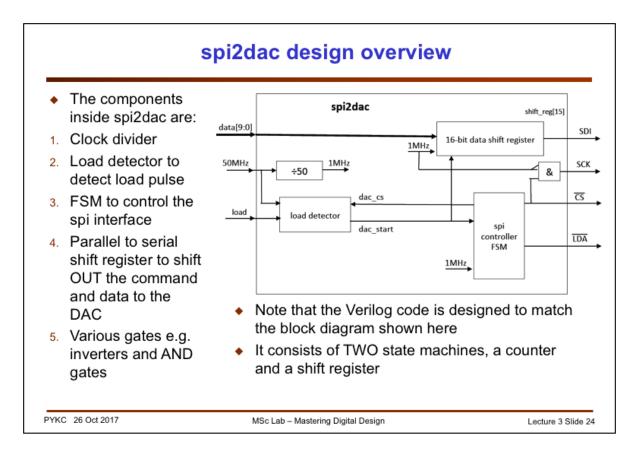

The interface between the FPGA chip and the converters is through the SPI bus. You are given the Verilog design for these two interface modules: spi2dac.v and spi2adc.v. In the rest of this lecture, I will be going through the design of the spi2dac module.

In order to use the DAC, you have to include the interface module "spi2dac" in your design. This module has a schematic shown above. It takes two inputs (in addition to the 50MHz clock signal): data[9:0] is the 10-bit digital data to be converted by the DAC, and a load signal which is a high pulse to trigger the spi2dac module to send the 10-bit data to the DAC.

The internal working of sp2dac can be divided into 4 main modules. The divide-by-50 module is straight forward – it produces a 1MHz clock for the finite state machine, and is gated through the AND gate to generate the serial clock signal (at 1MHz).

The load detector module handles the load command and produces control signals to the SPI state machine and the shift register.

The shift register sends the control bits and the 10-bit data serially to the SDI output. The spi controller FSM is the main control module designed as a state machine.

We will consider each sub-module individually in next week's lecture.